# 2.1 8086 Microprocessor (µp):

The main features of 8086 µp are:

- 1. It is a 16-bit Microprocessor (μp). It's ALU, internal registers works with 16bit binary word.

- 2. 8086 has a 20 bit address bus can access up to 220= 1 MB memory locations.

- 3. 8086 has a 16bit data bus. It can read or write data to a memory/port either 16bits or 8 bit at a time.

- 4. It can support up to 64K I/O ports.

- 5. Frequency range of 8086 is 6-10 MHz.

- 6. It has multiplexed address and data bus AD0- AD15 and A16 A19.

- 7. It can pre-fetch up to 6 instruction bytes from memory and queues them in order to speed up instruction execution.

- 8. It requires +5V power supply.

- 9. A 40 pin dual in line package.

- 10.8086 is designed to operate in two modes, Minimum mode and Maximum mode.

- a. The minimum mode is selected by applying logic 1 to the  $MN/\overline{MX}$  input pin. This is a single microprocessor configuration.

- b. The maximum mode is selected applying by logic 0 to the  $MN/\overline{MX}$ input This multi-microprocessors pin. is a configuration.

# 2.2 Architecture or Functional Block Diagram of 808<mark>6</mark>:

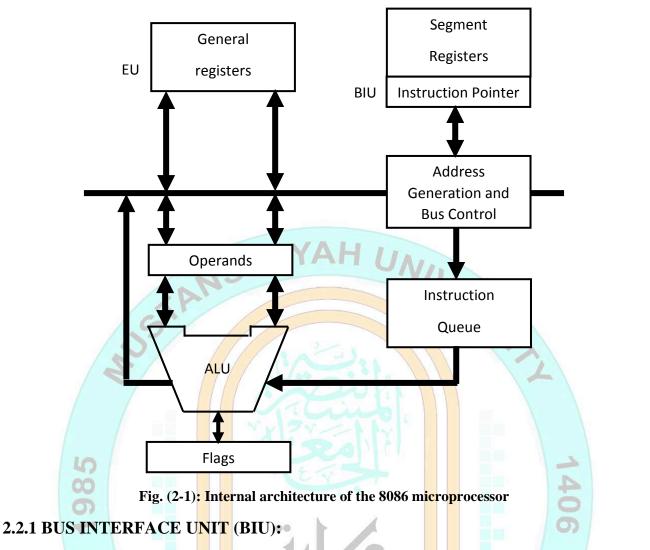

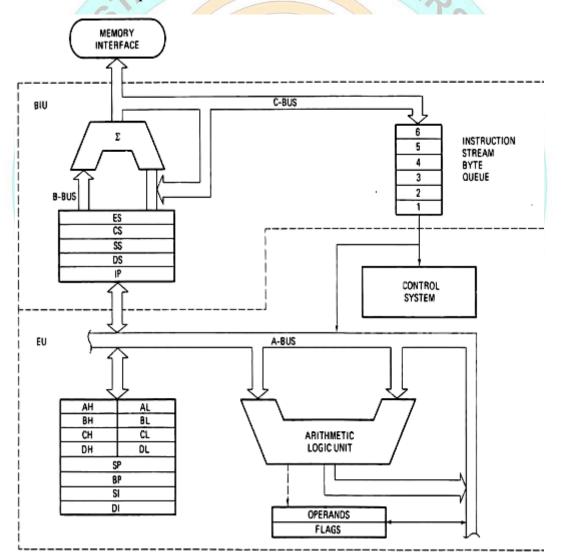

of a is processor its micro-architecture internal architecture-that The is. implement the the circuit building blocks that software and hardware of microprocessors. The architectures the 8086 micro-architecture of the 8086 microprocessors employs parallel processing-that is. they are implemented with several simultaneously operating processing units. the internal of the Figure 2-1 shows architecture 8086 microprocessors. They contain two processing units: the Bus Interface Unit (BIU) and the Execution Unit (EU).

- 1. It provides a full 16 bit bidirectional data bus and 20 bit address bus.

- 2. The bus interface unit connects the microprocessor to external devices. BIU performs following operations:

- a. Instruction fetching.

- b. Reading and writing data of data operands for memory.

- c. Inputting/outputting data for input/output peripherals.

- d. And other functions related to instruction and data acquisition.

- 3. To implement above functions, the BIU contains the segment registers, the instruction pointer, address generation adder, bus control logic, and an instruction queue.

- 4. The BIU uses a mechanism known as an instruction stream queue to implement pipeline architecture.

# 2.2.2 EXECUTION UNIT (EU):

- 1. The Execution unit is responsible for decoding and executing all instructions.

- 2. The EU consists of arithmetic logic unit (ALU), status and control flags, general-purpose registers, and temporary-operand registers.

- 3. The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operands if necessary, passes them to the requests perform read write BIU and it to the or by cycles to perform or I/O and the operation specified by the memory instruction on the operands.

- 4. During the execution of the instruction, the EU tests the status and control flags and updates them based on the results of executing the instruction.

## 2.3 Internal Microprocessor Architecture:

Before a program is written or any instruction investigated, the internal configuration of the microprocessor must be known.

Fig. (2-2): Software Model of the 8086 microprocessor.

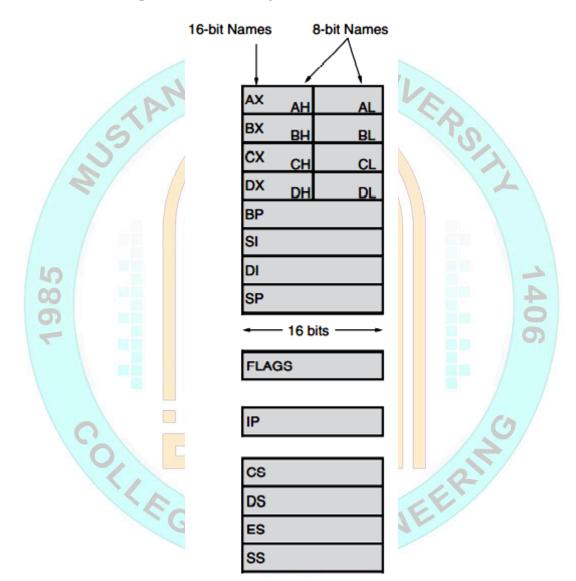

# 2.4 The Programming Model

The programming model of the 8086 microprocessor is considered to be program visible because its registers are used during application programming and are specified by the instructions. Other registers are invisible considered to be program because they addressable are not directly during applications programming, used indirectly but may be programming. during system Figure 2 - 3illustrates the programming model of the 8086 microprocessor including the 16-bit extensions.

Fig. (2–3): The programming model of the 8086 microprocessor including the 16-bit extensions.

The 8-bit registers are AH, AL, BH, BL, CH, CL, DH, and DL and are referred instruction is using to when an formed these two-letter designations. For example, an ADD AL,AH instruction adds the 8-bit contents of AH to AL. (Only AL changes due to this instruction.) The 16bit registers are AX, BX, CX, DX, SP, BP, DI, SI, IP, FLAGS, CS, DS, ES, SS, FS, and GS. Note that the first 4 16 registers contain a pair of 8-An example is AX, which contains AH and AL. bit registers. The 16-bit registers referenced with the two-letter designations such AX. For are as The Microprocessor and its Architecture

example, an ADD DX, CX instruction adds the 16-bit contents of CX to DX. (Only DX changes due to this instruction).

**1.** The multipurpose registers include AX, BX, CX, DX, BP, DI, and SI. These registers hold various data sizes (bytes or words) and are used for almost any purpose, as dictated by a program.

#### **General Purpose Registers**

|             |    | 15 ( | )                              |

|-------------|----|------|--------------------------------|

| Accumulator | AX |      | Multiply, divide, I/O          |

| Base        | ΒX |      | pointer to base address "data" |

| Count       | СХ |      | Count for loops, shifts        |

| Data        | DX |      | Multiply, divide, I/O          |

|             |    | DIAN |                                |

AX is referenced AX (accumulator): 16-bit register as a (AX), or as either of two 8-bit registers (AH and AL). The accumulator is used for such as multiplication, division, and instructions some of the adjustment instructions. For these instructions, the accumulator has a special purpose, but is generally considered to be a multipurpose register.

**BX** (Base Index): BX is referenced as a 16-bit register (BX), or as either of two 8-bit registers (BH and BL). The BX register (base index) sometimes holds the offset address of a location in the memory system in all versions of the microprocessor.

CX (count): CX is referenced as a 16-bit register (CX), as either of or two 8-bit registers (CH and CL). CX is a general-purpose register that the various instructions also holds count for also can address memory Instructions use count are repeated string data. that a the instructions. loop instructions. The shift. rotate, and shift and rotate instructions use CL the repeated as the count, string instructions use CX. and the LOOP/LOOPD instructions use CX.

**DX** (data): DX is referenced as a 16-bit register (DX), or as either of two 8-bit registers (DH and DL). DX is a general-purpose register that holds a part of the result from a multiplication or part of the dividend before a division.

# Pointer and Index Registers

|                   |    | 15 0 |   |

|-------------------|----|------|---|

| Stack Pointer     | SP |      | F |

| Base pointer      | ΒP |      |   |

| Source Index      | SI |      | S |

| Destination Index | DI |      | [ |

Pointer to top of stack Pointer to base address (stack) Source string/index pointer Destination string/index pointer

**BP** (base pointer): BP points to a memory location in all versions of the microprocessor for memory data transfers.

**DI** (destination index): DI often addresses string destination data for the string instructions.

SI (source index): The source index register often addresses source SI string data for the string instructions. Like DI, also functions as а general-purpose register.

**2.** The Special-Purpose Registers include IP, SP, and FLAGS; and the segment registers include CS, DS, ES, SS, FS, and GS.

**IP** (instruction pointer): IP addresses the next instruction in a section of memory defined as a code segment. The instruction pointer, which points to the next instruction in a program, is used by the microprocessor to find sequential instruction program located within the next in a the code segment. The instruction pointer can be modified with a jump call or а instruction.

**SP** (Stack pointer): SP addresses an area of memory called the stack. The stack memory stores data through this pointer and is explained later in the text with the instructions that address stack data.

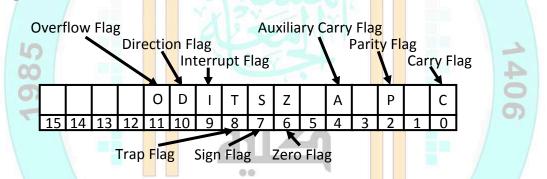

**FLAGS:** FLAGS indicate the condition of the microprocessor and control its operation. Figure 2–4 shows the flag registers of all versions of the microprocessor.

Fig. (2–4): The FLAG register counts for the entire 8086 microprocessor.

C (carry): Carry holds the carry after addition or the borrow after subtraction. The carry flag also indicates error conditions, as dictated by some programs and procedures.

**P** (parity): Parity is a logic 0 for odd parity and a logic 1 for even parity. Parity is the count of ones in a number expressed as even or odd. For example, if a number contains three binary one bits, it has odd parity. If a number contains no one bits, it has even parity. The parity flag finds little application in modern programming and was implemented in early Intel checking microprocessors for data in data communications environments. accomplished checking is often Today parity by the data communications equipment instead of the microprocessor.

A (auxiliary carry): The auxiliary carry holds the carry (half-carry) after addition or the borrow after subtraction between bit positions 3 and 4 of the result. This highly specialized flag bit is tested by the DAA and DAS instructions to adjust the value of AL after a BCD addition or subtraction.

Otherwise, the A flag bit is not used by the microprocessor or any other instructions.

**Z** (zero): The zero flag shows that the result of an arithmetic or logic operation is zero. If Z=1, the result is zero; if Z=0, the result is not zero. This may be confusing, but that is how Intel decided to name this flag.

**S** (sign): The sign flag holds the arithmetic sign of the result after an arithmetic or logic instruction executes. If S=1, the sign bit (leftmost bit of a number) is set or negative; if S=0, the sign bit is cleared or positive.

trap flag enables trapping Т (trap): The through an on-chip debugging feature. (A program is debugged to find an error or bug.) If the T flag is microprocessor interrupts the flow of the enabled (1). the program on conditions as indicated by the debug registers and control registers. If the T flag is a logic 0, the trapping (debugging) feature is disabled.

I (interrupt): The interrupt flag controls the operation of the INTR (interrupt request) input pin. If I=1, the INTR pin is enabled; if I=0, the INTR pin is disabled. The state of the I flag bit is controlled by the STI (set I flag) and CLI (clear I flag) instructions.

D The selects either (direction): direction flag the increment or decrement mode the DI and/or SI registers during string instructions. for are automatically decremented; if D=0, If D=1, the registers the registers automatically incremented. The flag with the STD are D is set (set direction) and cleared with the CLD (clear direction) instructions.

occur when signed Overflows 0 (overflow): numbers are added or subtracted. indicates that the result An overflow has exceeded the For example, if 7FH capacity of the machine. (+127)is added—using an (-128). This (+1). result is 80H 8-bit addition-to 01H the \_ result condition indicated by an overflow [ the overflow represents flag for signed addition. For unsigned operations, the overflow flag is ignored.

3. **Registers.** Additional registers, called segment Segment registers. combined with other addresses when registers in generate memory the microprocessor. A segment register functions differently in the real mode when compared to the protected mode operation of the microprocessor.

#### Segment Registers

CS (code): The code segment is a section of memory that holds the code procedures) used by microprocessor. code (programs and the The segment register defines the starting address of the section of memory

holding code. In real mode operation, it defines the start of a 64K byte section of memory; in protected mode, it selects a descriptor that describes the starting address and length of a section of memory holding code.

DS (data): The data segment is a section of memory that contains most accessed in the data segment by data used by a program. Data are an offset address or the contents of other registers that hold the offset with address. As the code segment and other segments, the length is limited to 64K bytes in the 8086.

**ES** (extra): The extra segment is an additional data segment that is used by some of the string instructions to hold destination data.

**SS (stack):** The stack segment defines the area of memory used for the stack. The stack entry point is determined by the stack segment and stack pointer registers. The BP register also addresses data within the stack segment.

## 2.5 Real Mode Memory Addressing:

The 8086 operate exclusively in the real mode operation which allows the to address only the first 1M byte of microprocessor memory space. Note that the first 1M byte of memory is called the real memory, conventional DOS mode memory, memory system. Real operation allows or application software written for the 8086, which only contains 1M byte of compatibility of software is memory. The upward partially responsible the continuing success of the Intel family of microprocessors. for In all cases, each of these microprocessors begins operation in the real mode by default whenever power is applied or the microprocessor is reset.

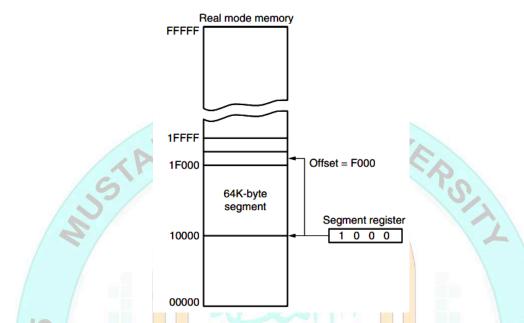

#### 2.5.1 Segments and Offsets

A combination of a segment address an offset address and accesses а memory location in the real mode. All real mode memory addresses must consist of a segment address plus an offset address. The segment address, located within one of the segment registers, defines the beginning address of any 64K-byte memory segment. The offset address selects any location within the 64K byte memory segment. Segments in the real mode always have a length of 64K bytes. Figure 2–5 shows how the segment plus scheme selects a memory location. Note that offset addressing the offset or displacement is the distance above the start of the segment.

the real mode. each **Paragraph:** In segment register is internally appended with a 0H on its rightmost end. This forms a 20-bit memory address, allowing it to access the start of a segment. The microprocessor must generate a 20-bit memory address a location within to access the

first 1Mof memory. For example, when segment register contains a memory beginning 1200H. addresses a 64K-byte segment location it at 12000H. Likewise, if a segment register contains 1201H. it addresses а segment beginning at location 12010H. Because of the internally memory appended OH, real mode segments can begin only at a 16-byte boundary in the memory system.

Fig. (2–5): The real mode memory-addressing scheme, using a segment address plus an offset.

Because a real mode segment of memory is 64K in length, the once ending address found by beginning address is known. the is adding if FFFFH. segment register contains 3000H. the For example, a first of the segment is 30000H, and the last address **3FFFFH**. address is or shows several examples of segment Table 2–1 register contents and the starting and ending addresses of the memory segments selected by each segment address.

The offset address, which is a part of the address, is added to the start of memory location within the memory the segment address a to segment. address is 1000H and the offset address For example, if the segment is 2000H. the microprocessor addresses memory location 12000H. The always added to the starting address of offset address is the segment to The segment and offset address is sometimes written the data. locate as 1000:2000 for a segment address of 1000H with an offset of 2000H.

addressing modes combine more offset Some than one register and an value to form an offset address. When this occurs, the sum of these values FFFFH. For example, the accessed may exceed address in a segment specified whose segment address is 4000H and whose offset address is as sum of F000H plus 3000H will location 42000H the access memory instead of location 52000H. When the F000H and 3000H are added. thev form a l6-bit (modulo 16) sum of 2000H used as the offset address; not

Note 12000H. the true sum. that the carry of 1 (F000H+3000H=12000H) this the offset dropped for addition to form address of 2000H. The is address is generated as 4000:2000 or 42000H.

| Segment Register | Starting Address | Ending Address |

|------------------|------------------|----------------|

| 2000H            | 20000H           | 2FFFFH         |

| 2001H            | 20010H           | 3000FH         |

| 2100H            | 21000H           | 30FFFH         |

| AB00H            | AB000H           | BAFFFH         |

| 1234H            | 12340H           | 2233FH         |

Table (2–1) Example of real mode segment addresses.

## 2.5.2 Default Segment and Offset Registers

microprocessor has a set of to The rules that apply segments whenever memory is addressed. These rules, which the real apply in mode, define segment register and offset register combination. For the the example, segment register always used code is with the instruction pointer to address the next instruction in a program. This combination is CS:IP, microprocessor's mode operation. The depending upon the of code segment register defines the start of the code segment and the instruction locates the instruction within pointer next the code segment. This combination (CS:IP) next executed locates the instruction by the microprocessor. For example, if CS=1400H and IP=1200H. the instruction microprocessor its next from memory fetches location 14000H+1200H or 15200H.

Another of the default combinations is the stack. Stack data are location referenced through the stack segment at the memory addressed pointer (SP) or the pointer (**BP**). These either the stack combinations by are referred to as SS:SP, or SS:BP. For example, if SS=2000H and BP=300H, microprocessor addresses memory location 23000H the for the that memory location. Note in real mode, segment only the stack of the extended register address rightmost 16 bits a location within the Other defaults are shown in Table 2–2 for memory segment. addressing memory using 8086 microprocessor with 16-bit registers.

| Segment | Offset                             | Special Purpose            |

|---------|------------------------------------|----------------------------|

| CS      | IP                                 | Instruction address        |

| SS      | SP or BP                           | Stack address              |

| DS      | BX, DI, SI, an 8- or 16-bit number | Data address               |

| ES      | DI for string instructions         | String destination address |

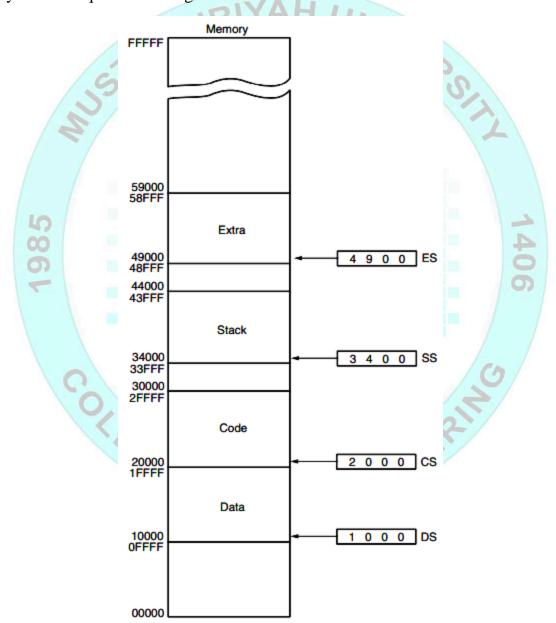

Figure 2–6 shows system that contains four memory segments. Note a that memory segment touch overlap if 64K bytes of a can or even memory are not required for a segment.

Fig. (2–6): A memory system showing the placement of four memory segments.