# Part (6)

## **CPU BASICS**

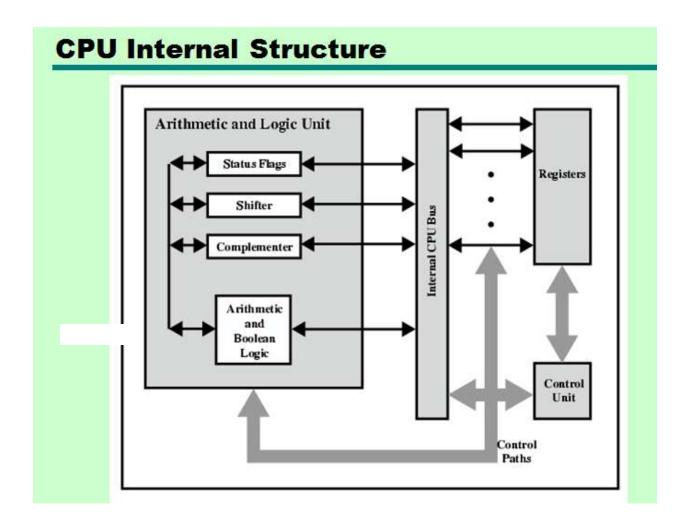

A typical CPU has three major components:

- 1- register set,

- 2- arithmetic logic unit (ALU),

- 3- control unit (CU).

The figure below shows the internal structure of the CPU .

The CPU fetches instructions from memory, reads and writes data from and to memory, and transfers data from and to input/output devices.

### Instruction execution cycle:

1- fetch: fetching next instruction( using PC) from memory into IR.

2-decode: decoding the instruction.

3- execute: executing the instruction.

### **REGISTER SET:**

• The register set differs from one computer architecture to another. It is usually a <u>combination of general-purpose and special purpose registers</u>

• *General-purpose registers* can be used for <u>multiple purposes</u> and assigned to a <u>variety of functions</u> by the programmer.

• Special-purpose registers are restricted to only specific functions.

### Memory Access Registers:

Two registers are essential in memory write and read operations: the memory data register (**MDR**) and memory address register (**MAR**). The MDR and MAR are <u>used exclusively by the CPU and are not directly accessible to</u> <u>programmers.</u>

In order to perform a **write** operation into a specified memory location, the MDR and MAR are used as follows:

**1.** The <u>word</u> to be stored into the memory location is first loaded by <u>the CPU</u> into **MDR**.

**2.** The <u>address of the location</u> into which the word is to be stored is loaded by the <u>CPU into a **MAR**</u>.

**3.** A <u>write signal is issued</u> by the CPU.

Similarly, to perform a memory **read** operation, the MDR and MAR are used as follows:

**1.** The <u>address</u> of the location from which the word is to be read is loaded <u>into the **MAR**</u>.

**2.** A <u>read signal is issued</u> by the CPU.

**3.** The required word will be loaded by the memory into the **MDR** ready for use by the CPU.

### **Instruction Fetching Registers:**

Two main registers are involved in fetching an instruction for execution: the program counter (**PC**) and the instruction register (**IR**). The PC is the register that <u>contains the address of the next instruction to be fetched</u>. The <u>fetched instruction is loaded in the IR</u>.

<u>**Condition Register:**</u> Program status word (**PSW**) register <u>contains bits</u> that are set by the CPU to indicate the current status of an executing program. These indicators are typically for arithmetic operations, interrupts,...etc.

#### **Special-Purpose Address Registers:**

• In index addressing, the **index register** holds an address displacement which when added to a constant, the address of the operand is obtained.

• A **segment register** holds the address of the base of the segment.

• A specific register, called the **stack pointer (SP**), is used to indicate the stack location that can be addressed. In the stack push operation, the SP is incremented and in pop operation the SP is decremented.

### **Register transfer:**

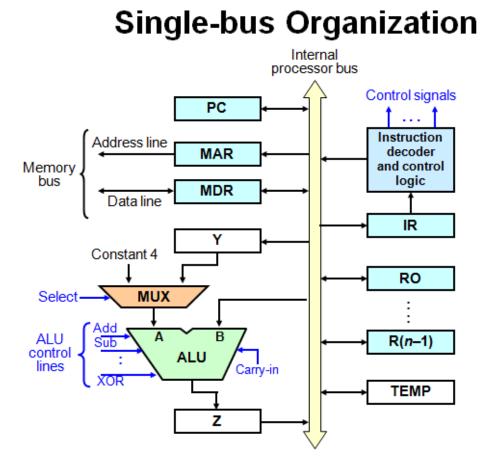

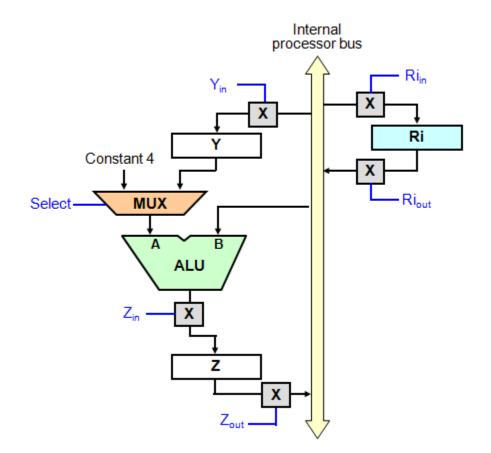

For each register Ri, there are two control signals:  $Ri_{in}$  used to load the data on the bus into the register.  $Ri_{out}$  used to place the register's contents on the bus.

EX: R1  $\rightarrow$  R4 will be R1\_out , R4\_in

### To perform arithmetic/logic operation:

.The ALU is a combinational circuit that has no internal storage.

•ALU gets the two operands from MUX and bus. The result is temporarily stored in register Z.

**EX:** What is the sequence of operation to the following instruction: ADD R1 , R2 **1.**  $R1_{out}$ ,  $Y_{in}$ **2.**  $R2_{out}$ , Select Y, Add,  $Z_{in}$ **3.**  $Z_{out}$ ,  $R2_{in}$

### Fetching aword from memory:

**EX:** MOVE (R1),R2

**1.** R1<sub>out</sub> ,MAR<sub>in</sub> , Read

2. WMF( wait to memory function complete)

3. MDRout ,R2in

### **Execution of a complete instruction:**

**EX:** Write the control steps to <u>fetch and execute</u> the following instruction:

ADD (R3), R1

Note:  $PC_{new} = PC_{old} + constant 4$

### **Execution of Branch instructions:**

A branch instruction replaces the content of PC with the:

branch target address( $PC_{new}$ ) = offset **X** +  $PC_{old}$  offset **X** (given in the branch instruction).

The required control steps to fetch and execute unconditional branch as follows:

- 1 PCout, MARin, Read, Select 4, Add, Zin

- 2 Z<sub>out</sub>, PC<sub>in</sub>, Y<sub>in</sub>, WMFC

- 3 MDR<sub>out</sub>, IR<sub>in</sub>

- 4 offset Xout, Select y, Add, Zin

- 5 Zout, PCin, End.

#### EX:

The required control steps to fetch and execute <u>a conditional</u> branch( **Br<0**) is illustrated bellow:

Note: N=0 (positive) N=1 ( negative)

- 1 PCout, MARin, Read, Select 4, Add, Zin

- 2 Zout, PCin, Yin, WMFC

- 3 MDR<sub>out</sub>, IR<sub>in</sub>

4 Branch to 25

- 25 If N=0 then branch to 1

- 26 offset Xout, Select y, Add, Zin

- 27 Z<sub>out</sub>, PC<sub>in</sub>, End.

H.W=Br > 0

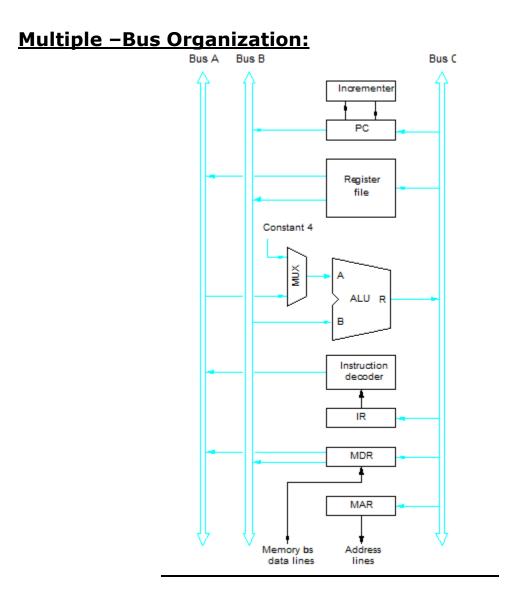

**Example:** Write the control steps to <u>fetch and execute</u> the following instruction in <u>multiple- bus CPU:</u>

- 1 PCout, R=B, MARin, Read, Inc PC

- 2 WMFC

- 3 MDRout **B**, R=B , IRin

- 4 R4<sub>out A</sub>, R5<sub>out B</sub>, Select A, Add, R6<sub>in</sub>, End.

**EX:** Write the control steps to <u>fetch and execute</u> the following instruction in <u>multiple- bus CPU:</u> **Add (R4), R5,R6**

PC<sub>out</sub>, R=B, MAR<sub>in</sub>, Read, Inc PC

WMFC

MDR<sub>out</sub> B, R=B, IR<sub>in</sub>

R4<sub>out</sub> B, R=B, MAR<sub>in</sub>, Read

WMFC

MDR<sub>out</sub> B, R5<sub>out</sub> A, Select A, Add, R6<sub>in</sub>, End.

#### **Control Unit:**

•The control unit is the main component that directs the system operation by sending control signals to the control buses.

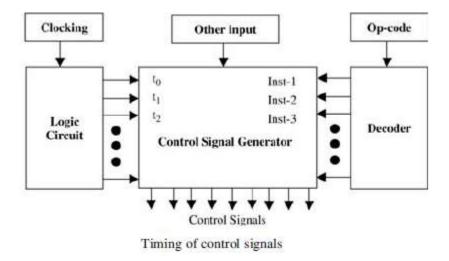

• The system clock produces a continuous sequence of pulses (t0, t1,t2...) in a specified duration and frequency .

• The <u>decoder</u> takes the op- code and provide the <u>control signal generator</u> with information about the instruction to be executed.

•The <u>logic circuit module</u> is used with <u>other inputs</u> to <u>generate control</u> <u>signals</u>.

• The signal generator can be specified simply by a <u>set of Boolean equations</u> for its output in terms of its inputs.

There are mainly two different types of control units: **micro programmed** and **hardwired**.

#### Hardwired control:

• Fixed logic circuits that correspond directly to the Boolean expressions are used to generate the control signals.

• Hardwired control is faster than micro programmed control.

• Hardwired control could <u>be very expensive</u> and complicated for complex systems, but <u>more economical</u> for small systems.

• Hardwired control will require <u>a redesign</u> of the entire systems in the case of any change.

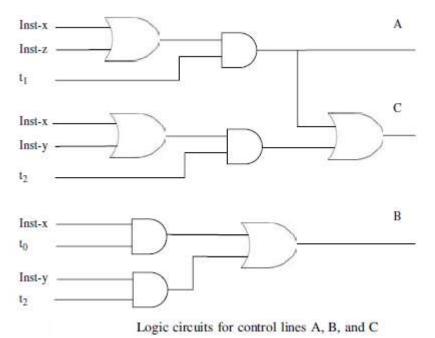

In hardwired control, a direct implementation is accomplished using logic circuits. For <u>each control line</u>, one must find the <u>Boolean expression in terms</u> <u>of the input</u> to the control signal generator .

**EX:** Assume that the instruction set of a machine has the <u>three</u> instructions: Inst-**x**, Inst-**y**, and Inst-**z**; and **A**, **B**, **C**, **D**, **E**, **F**,**G**, and **H** are control lines. The following table shows the control lines that should be activated for the three instructions at the three steps t0 , t1 , and t2 .

| Step                  | Inst-x  | Inst-y  | Inst-z  |  |  |  |  |

|-----------------------|---------|---------|---------|--|--|--|--|

| t <sub>0</sub>        | D, B, E | F, H, G | E, H    |  |  |  |  |

| <i>t</i> <sub>1</sub> | C, A, H | G       | D, A, C |  |  |  |  |

| <i>t</i> <sub>2</sub> | G, C    | B, C    |         |  |  |  |  |

The Boolean expressions for control lines A, B, and C can be obtained as follows

$$A = \text{Inst-x} \cdot t_1 + \text{Inst-z} \cdot t_1 = (\text{Inst-x} + \text{Inst-z}) \cdot t_1$$

$$B = \text{Inst-x} \cdot t_0 + \text{Inst-y} \cdot t_2$$

$$C = \text{Inst-x} \cdot t_1 + \text{Inst-x} \cdot t_2 + \text{Inst-y} \cdot t_2 + \text{Inst-z} \cdot t_1$$

$$= (\text{Inst-x} + \text{Inst-z}) \cdot t_1 + (\text{Inst-x} + \text{Inst-y}) \cdot t_2$$

The figure below shows the logic circuits for these control lines. Boolean expressions for the rest of the control lines can be obtained in a similar way.

### Micro programmed Control Unit

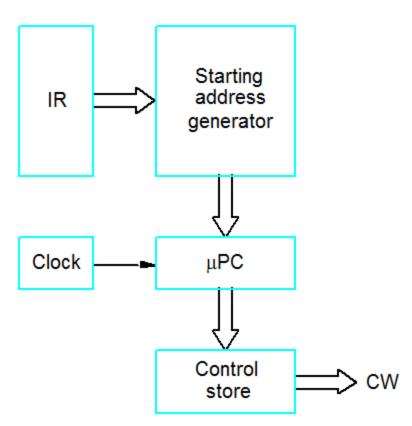

• The idea of micro programmed control <u>is to store the control signals</u> <u>associated with the implementation of an instruction as a **micro program** <u>in a special memory called a **control memory (CM)**.</u></u>

• A **control word** is a <u>microinstruction</u> that specifies one or more micro operations(control signals).

• A sequence of microinstructions is called a *micro program*

• It should also be noted that micro programmed control <u>could adapt easily</u> to changes in the system design. We can easily add new instructions without changing hardware

• A **microinstruction** is a vector of bits, where <u>each bit is a control signal</u>, <u>condition code</u>, <u>or the address of the next microinstruction</u>.

• When an instruction is fetched from memory, the <u>op-code is mapped to a</u> <u>microinstruction address in the control memory</u>.

• The microinstruction processor uses that <u>address to fetch the first</u> <u>microinstruction in the micro program</u>.

•After fetching each microinstruction, the <u>appropriate control lines will be</u> <u>enabled</u>. Every control line that corresponds to a "1" bit should be turned on. Every control line that corresponds to a "0" bit should be left off.

•After completing the execution of one microinstruction, a new microinstruction will be fetched and executed .In the following is an example of a **micro program**:

- 1 PCout, MARin, Read, Select 4, Add, Zin

- 2 Z<sub>out</sub>, PC<sub>in</sub>, Y<sub>in</sub>, WMFC

- 3 MDR<sub>out</sub>, IR<sub>in</sub>

- 4 Branch to 25

- 25 If N=0 then branch to 1

- $26 \quad offset \ X_{out}, \ Select \ y, \ Add, \ Z_{in}$

- 27 Z<sub>out</sub>, PC<sub>in</sub>, End.

#### **Horizontal Versus Vertical Microinstructions**

Micro instructions can be classified as *horizontal* or *vertical*:

<u>Individual bits in **horizontal** microinstructions correspond to individual</u> <u>control lines</u>. Horizontal microinstructions are long and allow maximum parallelism since <u>each bit controls a single control line</u>.

In **vertical** microinstructions, <u>control lines are coded into specific fields</u> <u>within a microinstruction</u>. Decoders are needed to map a field of k bits to 2<sup>k</sup> possible combinations of control lines. For example, <u>a 3-bit field in a</u> <u>microinstruction could be used to specify any one of eight possible lines</u>.

<u>Because of the encoding</u>, vertical microinstructions are much <u>shorter</u> than horizontal ones. Control lines encoded in the same field <u>cannot be activated</u> <u>simultaneously</u>. Therefore, vertical microinstructions allow only limited parallelism.

- Example of a horizontal organization scheme:

- 1. PC<sub>out</sub>, MAR<sub>in</sub>, Read, Select4, Add, Z<sub>in</sub>

- 2. Z<sub>out</sub>, PC<sub>in</sub>, Y<sub>in</sub>, WMFC

- 3. MDR<sub>out</sub>, IR<sub>in</sub>

- 4. (R3<sub>out</sub>, MAR<sub>in</sub>, Read)

- 5. R1<sub>out</sub>, Y<sub>in</sub>, WMFC

- 6. MDR<sub>out</sub>, SelectY, Add, Z<sub>in</sub>

- 7. Z<sub>out</sub>, R1<sub>in</sub>, End

| Micro-<br>instruction |   | PC.<br>PC | PC <sub>out</sub> | MAR <sub>in</sub> | Read | MDR <sub>out</sub> | IR <sub>in</sub> | ۲<br>'n | Select | Add | Z <sub>in</sub> | Zout | R1 <sub>out</sub> | Р <mark>.</mark> | R3 <sub>out</sub> | WMFC | End |   |

|-----------------------|---|-----------|-------------------|-------------------|------|--------------------|------------------|---------|--------|-----|-----------------|------|-------------------|------------------|-------------------|------|-----|---|

| 1                     |   | 0         | 1                 | 1                 | 1    | 0                  | 0                | 0       | 1      | 1   | 1               | 0    | 0                 | 0                | 0                 | 0    | 0   | D |

| 2                     | ( | 1         | 0                 | 0                 | 0    | 0                  | 0                | 1       | 0      | 0   | 0               | 1    | 0                 | 0                | 0                 | 1    | 0   | D |

| 3                     |   | 0         | 0                 | 0                 | 0    | 1                  | 1                | 0       | 0      | 0   | 0               | 0    | 0                 | 0                | 0                 | 0    | 0   | D |

| 4                     |   | 0         | 0                 | 1                 | 1    | 0                  | 0                | 0       | 0      | 0   | 0               | 0    | 0                 | 0                | 1                 | 0    | 0   | D |

| 5                     |   | 0         | 0                 | 0                 | 0    | 0                  | 0                | 1       | 0      | 0   | 0               | 0    | 1                 | 0                | 0                 | 1    | 0   | D |

| 6                     | ( | 0         | 0                 | 0                 | 0    | 1                  | 0                | 0       | 0      | 1   | 1               | 0    | 0                 | 0                | 0                 | 0    | 0   | D |

| 7                     |   | 0         | 0                 | 0                 | 0    | 0                  | 0                | 0       | 0      | 0   | 0               | 1    | 0                 | 1                | 0                 | 0    | 1   | D |

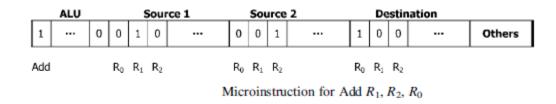

Select=0: SelectY Select=1: Select4 **Example**: Consider the three-bus data path shown in the figure below. In addition to the PC, IR, MAR, and MDR, assume that there are **16** general-purpose registers numbered R0–R15 . Also, assume that the ALU supports **eight** functions (add, subtract, multiply, divide, AND, OR, shift left, and shift right). Consider the add operation **Add R1**, **R2**, **R0**, which adds the contents of source registers R1 , R2 , and store the results in destination register R0 .

The format of the microinstruction under **horizontal** organization:

The format of the microinstruction under **vertical** organization:

| ALU Source 1 |   |   |   |           |  |  |  | So        | urce | 2 |  |  | 0           |  |  |  |  |  |        |

|--------------|---|---|---|-----------|--|--|--|-----------|------|---|--|--|-------------|--|--|--|--|--|--------|

| 0            | 0 | 0 | 1 | 1 0 0 0 0 |  |  |  | 1 0 0 0 1 |      |   |  |  | 0 0 0 0 0 0 |  |  |  |  |  | Others |

Microinstruction for Add R1, R2, R0