### Two basic memory operations

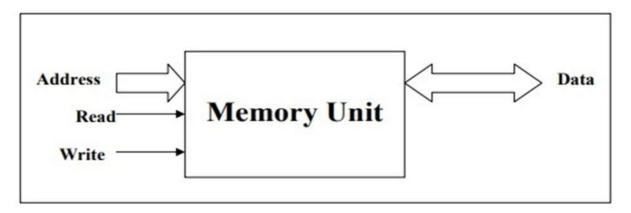

The memory unit supports two fundamental operations: Read and Write. The read operation read a previously stored data and the write operation stores a value in memory. See Figure 4

Figure 4: Block diagram of system memory

#### Steps in a typical read cycle

| Place the address of the location to be read on the address bus. |

|------------------------------------------------------------------|

| Activate the memory read control signal on the control bus.      |

| Wait for the memory to retrieve the data from the address memory |

| location.                                                        |

| Read the data from the data bus.                                 |

| Drop the memory read control signal to terminate the read cycle. |

## Steps in a typical write cycle

- o Place the address of the location to be written on the address bus.

- o Place the data to be written on the data bus.

- o Activate the memory write control signal on the control bus.

- Wait for the memory to store the data at the address location.

- o Drop the memory write control signal to terminate the write cycle.

#### Addresses

Group of bits which are arranged sequentially in memory, to enable direct access, a number called address is associated with each group. Addresses start at 0 and increase for successive groups. The term location refers to a group of bits with a unique address. Table 1 represents Bit, Byte, and Larger units.

Number of Byte Name Bit 0 or 1 is a group of bits used to represent a character, **Byte** typically 8-bit. Word 2-bytes (16-bit) data item **Double Word** 4-byte (32-bits) 8-Bytes (64-bit) Quadword 16-bytes (128-bit) Paragraph the number  $2^{10} = 1024 = 1$ K for KiloByte, (thus KiloByte (KB) 640K = 640 \* 1024 = 655360 bytes)

Table1: Bit, Byte, and Larger units.

# Types of memory

The memory unit can be implemented using a variety of memory chipsdifferent speeds, different manufacturing technology, and different sizes. The two basic types are RAM and ROM.

1. **Read Only Memories (ROM):** ROMs allow only read operation to be performed. This memory is non-volatile. Most ROMs are programmed and cannot be altered.

This type of ROM is cheaper to manufacture than other types of ROM. The program that controls the standard I/O functions (called BIOS) is kept in ROM, configuration software.

#### Other types of ROM include

- ♣ Programmable ROM (PROM).

- ♣ Erasable PROM (EPROM) is read only memory that can be reprogrammed using special equipment.

- ♣ EAPROM, Electrically Alterable Programmable ROM is a Read Only Memory that is electrically reprogrammable.

## **Read/Write Memory**

Read/Write memory is commonly referred to as Random Access Memory (RAM), it is divided into **static** and **dynamic**.

## **Static RAM (SRAM)**

- used for implementing CPU registers and cache memories.

- used for special high speed memory called cache memory which greatly improves system performance. Static RAM keeps its value without having to be refreshed.

## **Dynamic RAM (DRAM)**

- the bulk of main memory in a typical computer system consists of dynamic ram.

- main memory, or RAM is where program, data are kept when a program is running. It must be refreshed with in less than a millisecond or losses its contents.

#### C. INPUT/OUTPUT

Input / Output (I/O) devices provide the means by which the computer system can interact with the outside world. Computers use I/O devices (also called peripheral devices) for two major purposes:

- 1. To communicate with the outside world and,

- 2. Store data.

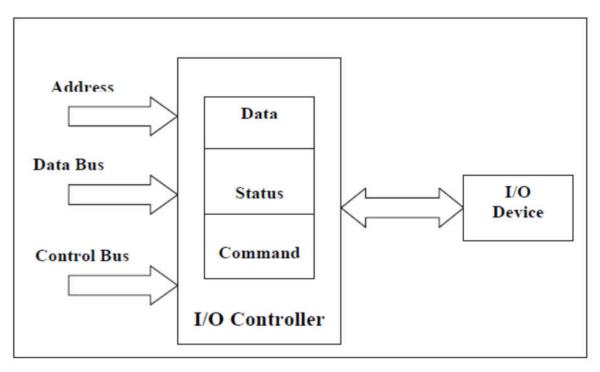

Devices that are used to communicate like, printer, keyboard, modem, Devices that are used to store data like disk drive. I/O devices are connected to the system bus through <u>I/O controller</u> (interface) – which acts as interface between the system bus and I/O devices.

## There are two main reasons for using I/O controllers

- 1. I/O devices exhibit different characteristics and if these devices are connected directly, the CPU would have to understand and respond appropriately to each I/O device. This would cause the CPU to spend a lot of time interacting with I/O devices and spend less time executing user programs.

- 2. The amount of electrical power used to send signals on the system bus is very low. This means that the cable connecting the I/O device has to be very short (a few centimeters at most). I/O controllers typically contain driver hardware to send current over long cable that connects I/O devices. See Figure 5.

Figure 5: Block diagram of a generic I/O device interface.

### **Evolution of Intel Microprocessor**

The principle way in which MPU & microcomputer are categorized in term of the maximum number of binary bit in the data they process that is, their **word length**. Processor vary in their speed, capacity of memory, register and data bus, below are a brief description of various Intel processor in Table 2.

8088 and 8086 functionally identical but 8088 lower performance, 80186 run all 8088 and 8086 software, but have 10 new instructions. 80188 in function is identical to 80186 but lower performance. 80286 run all 8086, 80186 program, but has extra instruction, more powerful than 8086. 83086 has various operation mode, which allow it to act as 80286 chip or multiple 8086 chip, as well as a set of instruction capable of 32 bit operations such as arithmetic.

6 Byte

80386

**Features Descriptions** Microprocessor Name Width of Width of Instruction (DB) (AB) queue length 8086 16 bit 20 bit 6 Byte 8080 8 bit 20 bit 4 Byte 80186 16 bit 20 bit 6 Byte 80188 8 bit 20 bit 4 Byte 24 bit 80286 16 bit 6 Byte

32 bit

**Table 2: Different Microprocessor features descriptions**

#### **Execution Unit and Bus Interface**

32 bit

Unit In the Figure 6, the processor is partitioned into two logical units: an **Execution Unit** (EU) and **Bus Interface Unit** (BIU). The role of the EU is to execute instruction, whereas the BIU delivers instruction and data to EU. The EU contains **ALU**, **CU** and number of **registers**. This feature enables the EU to execute instructions and perform arithmetic and logical operations. The most important function of BIU is to manage the bus control unit, segment registers instruction queue. The BIU controls the busses that transfer data to the EU, to memory, and to external input/output devices, whereas the segment registers control the memory addressing.

Another function of the BIU is to provide access to instructions, because the instructions for a program that is executing are kept in memory, the BIU must access instruction from memory and place them in an instruction queue, which varies in size depending on the processor. This feature enables the BIU to look ahead and prefetch instructions, so that there is always a queue of instructions ready to execute.

The EU and BIU work in parallel, with the BIU keeping one step ahead. The EU notifies the BIU when it needs access to data in memory or I/O devices. Also the EU request machine code instructions from the BIU instruction queue. The top instruction is the currently executable one, and while the EU is occupied executing an instruction, the BIU fetch another instruction from memory. This fetching overlaps with execution and speeds up processing.